- Retrait gratuit dans votre magasin Club

- 7.000.000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

- Retrait gratuit dans votre magasin Club

- 7.000.0000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

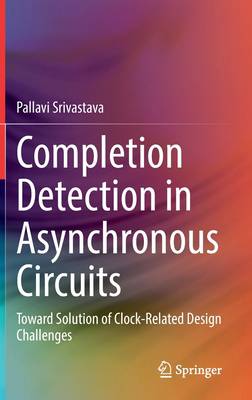

Completion Detection in Asynchronous Circuits

Toward Solution of Clock-Related Design Challenges

Pallavi SrivastavaDescription

This book is intended for designers with experience in traditional (clocked) circuit design, seeking information about asynchronous circuit design, in order to determine if it would be advantageous to adopt asynchronous methodologies in their next design project. The author introduces a generic approach for implementing a deterministic completion detection scheme for asynchronous bundled data circuits that incorporates a data-dependent computational process, taking advantage of the average-case delay. The author validates the architecture using a barrel shifter, as shifting is the basic operation required by all the processors. The generic architecture proposed in this book for a deterministic completion detection scheme for bundled data circuits will facilitate researchers in considering the asynchronous design style for developing digital circuits.

Spécifications

Parties prenantes

- Auteur(s) :

- Editeur:

Contenu

- Nombre de pages :

- 119

- Langue:

- Anglais

Caractéristiques

- EAN:

- 9783031183966

- Date de parution :

- 10-11-22

- Format:

- Livre relié

- Format numérique:

- Genaaid

- Dimensions :

- 156 mm x 234 mm

- Poids :

- 371 g

Les avis

Nous publions uniquement les avis qui respectent les conditions requises. Consultez nos conditions pour les avis.