En raison d'une grêve chez bpost, votre commande pourrait être retardée. Vous avez besoin d’un livre rapidement ? Nos magasins vous accueillent à bras ouverts !

- Retrait gratuit dans votre magasin Club

- 7.000.000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

En raison de la grêve chez bpost, votre commande pourrait être retardée. Vous avez besoin d’un livre rapidement ? Nos magasins vous accueillent à bras ouverts !

- Retrait gratuit dans votre magasin Club

- 7.000.0000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

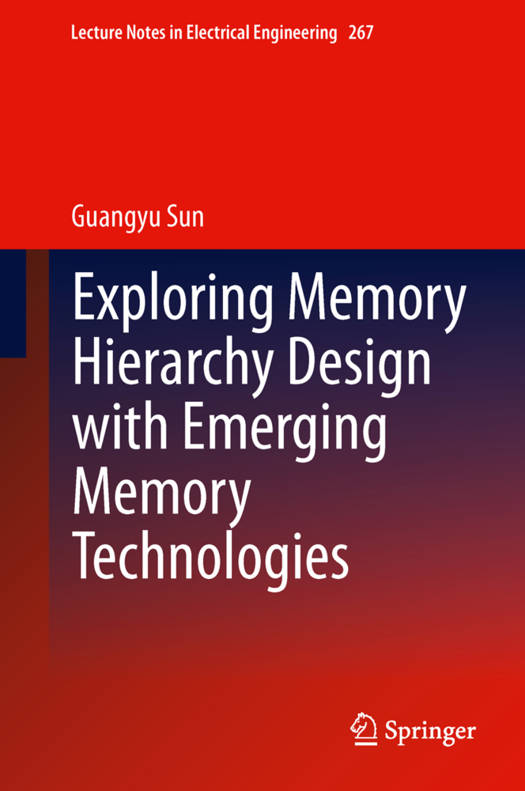

Exploring Memory Hierarchy Design with Emerging Memory Technologies

Guangyu Sun

105,45 €

+ 210 points

Format

Description

This book equips readers with tools for computer architecture of high performance, low power, and high reliability memory hierarchy in computer systems based on emerging memory technologies, such as STTRAM, PCM, FBDRAM, etc. The techniques described offer advantages of high density, near-zero static power, and immunity to soft errors, which have the potential of overcoming the "memory wall." The authors discuss memory design from various perspectives: emerging memory technologies are employed in the memory hierarchy with novel architecture modification; hybrid memory structure is introduced to leverage advantages from multiple memory technologies; an analytical model named "Moguls" is introduced to explore quantitatively the optimization design of a memory hierarchy; finally, the vulnerability of the CMPs to radiation-based soft errors is improved by replacing different levels of on-chip memory with STT-RAMs.

Spécifications

Parties prenantes

- Auteur(s) :

- Editeur:

Contenu

- Nombre de pages :

- 122

- Langue:

- Anglais

- Collection :

- Tome:

- n° 267

Caractéristiques

- EAN:

- 9783319006802

- Date de parution :

- 02-10-13

- Format:

- Livre relié

- Format numérique:

- Genaaid

- Dimensions :

- 160 mm x 234 mm

- Poids :

- 317 g

Les avis

Nous publions uniquement les avis qui respectent les conditions requises. Consultez nos conditions pour les avis.