- Retrait gratuit dans votre magasin Club

- 7.000.000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

- Retrait gratuit dans votre magasin Club

- 7.000.0000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

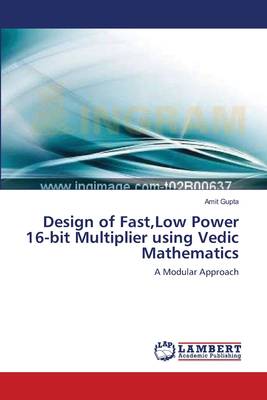

Design of Fast, Low Power 16-bit Multiplier using Vedic Mathematics

A Modular Approach

Amit Gupta

Livre broché | Anglais

58,45 €

+ 116 points

Description

Low power, high speed binary multiplier is an essential component of digital computers. Many architectures of multiplier based on Booth multiplication and array multiplication algorithms have been implemented. The array multiplier using Wallace tree structure is reported to be fastest and requiring minimum hardware. The speed of a binary multiplier is dominantly determined by the speed of adders used in the multiplier. This work describes a new 20-transistor low power high speed hybrid CMOS full adder and a new carry skip adder suitable for use in multipliers. A new modular design method for design of n x n multipliers using Vedic algorithm for multiplication has been proposed. The proposed design method uses more number of gates than array multiplier using Wallace tree but offers the advantages of simple and systematic interconnection scheme and maximum design reuse.

Spécifications

Parties prenantes

- Auteur(s) :

- Editeur:

Contenu

- Nombre de pages :

- 156

- Langue:

- Anglais

Caractéristiques

- EAN:

- 9783659171192

- Date de parution :

- 07-07-12

- Format:

- Livre broché

- Format numérique:

- Trade paperback (VS)

- Dimensions :

- 152 mm x 229 mm

- Poids :

- 235 g

Les avis

Nous publions uniquement les avis qui respectent les conditions requises. Consultez nos conditions pour les avis.