- Retrait gratuit dans votre magasin Club

- 7.000.000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

- Retrait gratuit dans votre magasin Club

- 7.000.0000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

Description

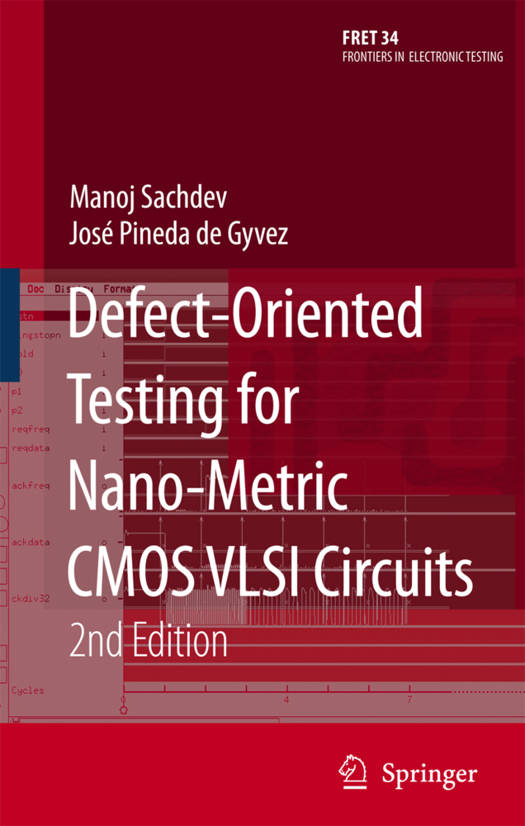

This book is essential to understand new test methodologies, algorithms and industrial practices. Without its insight into the physics of nano-metric technologies, it would be difficult to develop system-level test strategies that yield a high IC fault coverage. The work on defect-oriented testing presented in the book is not final, and it is an evolving field with interesting challenges imposed by the ever-changing nature of nano-metric technologies. The 2nd edition of Defect Oriented Testing has been extensively updated with the addition of chapters on Functional, Parametric Defect Models and Inductive fault Analysis and Yield Engineering to provide a link between defect sources and yield. Test and design practitioners from academia and industry will find that Defect-Oriented Testing for Nano-Metric CMOS VLSI Circuits lays the foundations for further pioneering work.

Spécifications

Parties prenantes

- Auteur(s) :

- Editeur:

Contenu

- Nombre de pages :

- 328

- Langue:

- Anglais

- Collection :

- Tome:

- n° 34

Caractéristiques

- EAN:

- 9781441942852

- Date de parution :

- 10-11-10

- Format:

- Livre broché

- Format numérique:

- Trade paperback (VS)

- Dimensions :

- 156 mm x 234 mm

- Poids :

- 494 g

Les avis

Nous publions uniquement les avis qui respectent les conditions requises. Consultez nos conditions pour les avis.